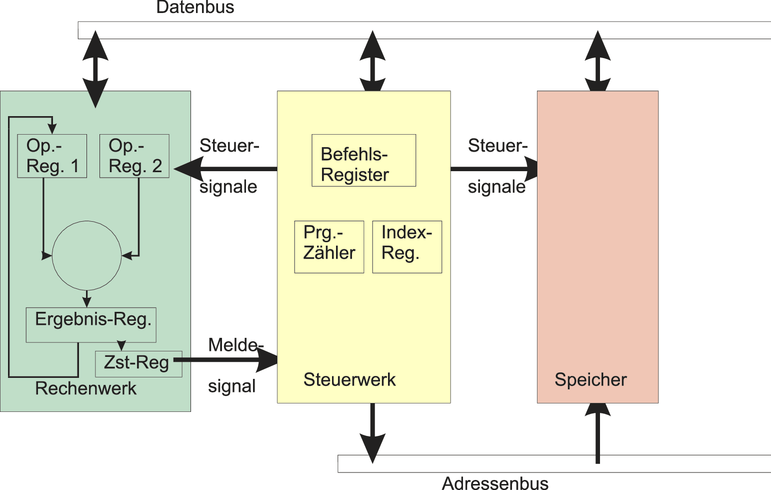

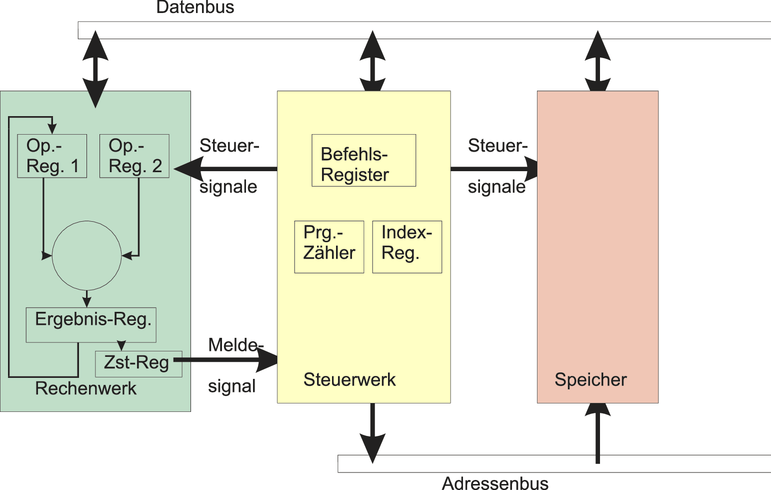

| Abbildung 2.72.: | von Neumannsche Struktur eines Computers. Abkürzungen: Op.-Reg.: Operationsregister; Ergebnis-Reg.: Ergebnisregister; Zst.-Reg.: Zustandsregister; Prg.-Zähler: Programmzähler; Index-Reg.: Indexregister |

Digitale Signalprozessoren sind eine Klasse von Mikroprozessoren, die für die Berechnung digitaler Filter optimiert worden sind.

Die Struktur eines klassischen Rechners nach John von Neumann[GJMW84] ist in der Abbildung 2.72 gezeigt. Bei dieser Computerarchitektur werden Programm und Daten im gleichen Speicher abgelegt. Daten werden über einen Datenbus vom Speicher zu dem Steuerwerk und dem Rechenwerk (oder umgekehrt) verschoben. Im Steuerwerk werden die Befehle aus dem Datenstrom dekodiert und in Steuersignale für das Rechenwerk oder den Speicher umgewandelt. Das Rechenwerk generiert, auch auf Grund von Rechenoperationen, die nächste Adresse.

| Abbildung 2.72.: | von Neumannsche Struktur eines Computers. Abkürzungen: Op.-Reg.: Operationsregister; Ergebnis-Reg.: Ergebnisregister; Zst.-Reg.: Zustandsregister; Prg.-Zähler: Programmzähler; Index-Reg.: Indexregister |

Der detailierte Ablauf einer Berechnung wird in Abbildung 2.73 gezeigt.

Abbildung 2.74 zeigt die Phasen der Ausführung eines Mikro-Maschinenbefehls in einem Mikroprozessor[Str98b]. Die Mikro-Maschinenbefehle werden in vier Phasen verarbeitet.

Moderne Prozessoren holen und dekodieren Adressen auf Vorrat. Während zeitintensive Befehle abgearbeitet werden, wir spekuliert, wie die Berechnung weitergehen könnte. Die modernen Mikroprozessoren haben einen beachtlichen Teil ihrer Leistung dieser Strategie zu verdanken.

Digitale Signalprozessoren unterscheiden Sich von klassischen Mikroprozessoren dadurch, dass sie mehrere Rechenwerke besitzen und dass diese so ausgelegt sind, dass die Operationen in einem Taktzyklus beendet werden. Ist dies nicht möglich, so sollte die Ausführungszeit eines Befehls vorherbestimmt sein.

Digitale Signalprozessoren werden für die folgenden Verfahren eingesetzt:

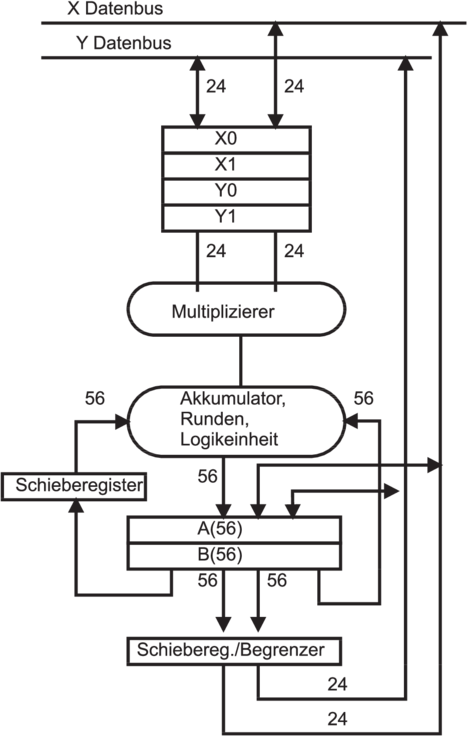

| Abbildung 2.76.: | Blockschaltbild des Ablaufs einer Rechenoperation im Motorola Signalprozessor DSP56001[Mot90] |

Anwendung finden die Signalprozessoren unter anderem in den folgenden Geräten:

Im Gegensatz zu einem klassischen Mikroprozessor hat ein DSP mehrere Daten- und Adressbusse (Abbildung 2.75 Diese Busse erlauben, in einem Taktzyklus mehrere Rechenoperationen gleichzeitig durchzuführen. Der Ablauf, der zum Beispiel in den Datenbüchern von Motorola[Mot90] sehr schön beschrieben ist, ist in Abbildung 2.76 gezeigt. Je zwei Register, X0 und X1, beziehungsweise Y0 und Y1, arbeiten auf einen Multiplizierer. Sie sind mit den jeweiligen datenbussen (X und Y) verbunden. Auf den Multiplizierer folgt der Addierer, so dass in den Ausgangsregistern zum Beispiel in einem Zyklus A = X0 ∗Y 0 + A steht. Schieberegister und Rundungseinheiten komplettieren die ALU (Arithmetic Logic Unit)

Die Multiplikation/Addition wird im Kern von einer MAC-Einheit durchgeführt (Abbildung 2.77). Die datenpfade haben eine unterschiedliche Breite. ein Vergleich mit den Gleichungen für IIR-Filter oder FIR-Filtern (Abschnitt 2.6.2 zeigt, dass die MAC-Einheit in einem Zyklus einen Knoten dieser Filtertypen berechnen kann. Tabelle H.1 zeigt eine Zusammenfassung von Benchmark-Ergebnissen für den DSP 56001 (Taktfrequenz 27 MHz) von Motorola. Ein Vergleich mit Mikroprozessoren wie der Intel-Familie zeigt, dass diese etwa die fünf- bis zehnfache Taktfrequenz brauchen bis sie eine FFT ebenso schnell wie ein DSP berechnen können.

Lizenzinformationen

Lizenzinformationen