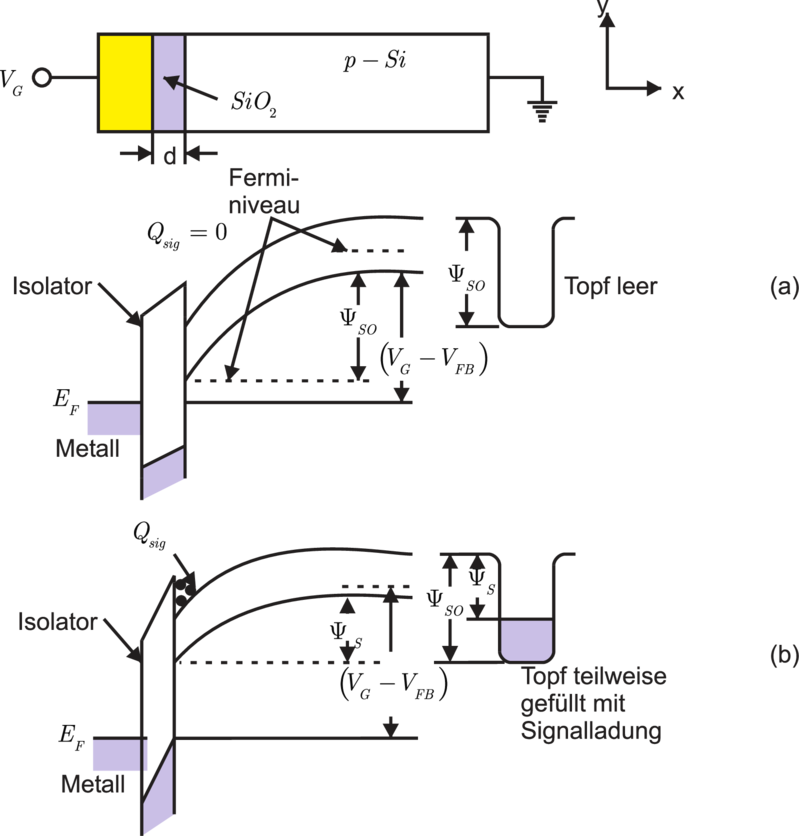

| Abbildung 3.45.: | Bänderschema einer MOS–Diode mit leerem Oberflächen–Leitungskanal (gezeichnet nach [Sze81]). |

Mit den besprochenen Kontaktphänomenen haben wir die Grundbausteine kennengelernt, aus denen alle Halbleiter–Bauelemente bestehen. Zuerst waren dies die bipolaren p–n–Dioden, danach die unipolaren Metall–Halbleiter– und Metall–Oxid–Halbleiter–Dioden. Letztere finden wir in den ‘ladungsgekoppelten’ CCDs, in den MOS–Transistoren und in den hoch– und höchstintegrierten Bausteinen (IC ‘integrated circuit’) für die Datenverarbeitung (Logik, Mikroprozessor, etc.) und die Speicherung (DRAM, etc.) wieder; allesamt auf Siliziumsubstraten. Bei den bipolaren Bauelementen sind herauszustellen die Transistoren und die grosse Vielfalt der optoelektrischen Bauelemente auf Basis der direkten Halbleiter, insbesonders auf der Grundlage von GaAs. Im folgenden also eine Auswahl aus dem oben genannten Themenbereich.

Das CCD in seiner einfachsten Form ist eine lineare Anordnung (‘linear array’) von dichtbenachbarten MOS–Dioden, deren Vorspannung so festgesetzt ist, dass an der Oberfläche eine ausgeprägte Verarmung an Majoritätsladungsträgern besteht (‘biased in deep surface depletion’).

| Abbildung 3.45.: | Bänderschema einer MOS–Diode mit leerem Oberflächen–Leitungskanal (gezeichnet nach [Sze81]). |

An dem bereits vom vorigen Kapitel gewohnten Beispiel des positiv vorgespannten Metall–p–Typ–Halbleiters sieht man im Bereich der Verarmungszone, dass sich im Leitungsband ein leerer Oberflächen–Leitungskanal (‘surface channel’) zwangsläufig ausgebildet hat. Bringt man in diesen zweidimensionalen Potentialtopf Elektronen, so sind diese zunächst in der Oberflächenschicht frei beweglich. Im realen MOS–Diodenbauelement ist die Metallelektrode natürlich nur endlich ausgedehnt; d. h. wir haben auch lateral in der Oberflächenschicht einen endlich ausgedehnten Potentialsee.

Legt man an die MOS–Kondensatoren–Kette mit Hilfe eines Taktgenerators (‘clock’) eine bestimmte Impulsfolge an, so kann elektrische Ladung in Form von Paketen kontrolliert an der Oberfläche eines Si–Substrats transportiert werden. Wir haben also die Grundstruktur eines dynamischen Analog–Schieberegisters vorliegen, wobei die Information in der Ladung QSignal steckt (und nicht, wie üblich, im Strom oder der Spannung). Neben seiner Anwendung als Schieberegister kann das CCD als Datenspeicher (mit Regenerationsstufen), als Verzögerungsglied, als Filter oder für logische Operationen eingesetzt werden.

Die verbreiteste Anwendung der CCD ist heute als Bildsensor (CCD–Kamera). In einem typischen Abstand von z. B. 7, 13 oder 27μm sitzen MOS–Dioden als optische Detektoren mit Grössen von z. B. 1, 7μm. In zweidimensionaler Anordnung erhält man so einen Bildsensor.

Beim optischen Detektor ist das Metall bzw. das Polysilizium meist transparent. Photonen, deren Energie grösser als die Energielücke des Si sind, generieren im Si ein Elektron–Loch–Paar. Das Loch diffundiert im Valenzband in die Tiefe des Si–Substrats, die Elektronen sammeln sich im n–Kanal an der Oberfläche. Das lichtempfindliche Bauelement kann im Prinzip aber auch eine Schottky–Diode, eine p–i–n–Fotodiode oder ein Fototransistor sein. Das CCD-Chip enthält aber in jedem Fall ein oder zwei MOS–Schieberegister zum Auslesen des bzw. der optischen Detektoren.

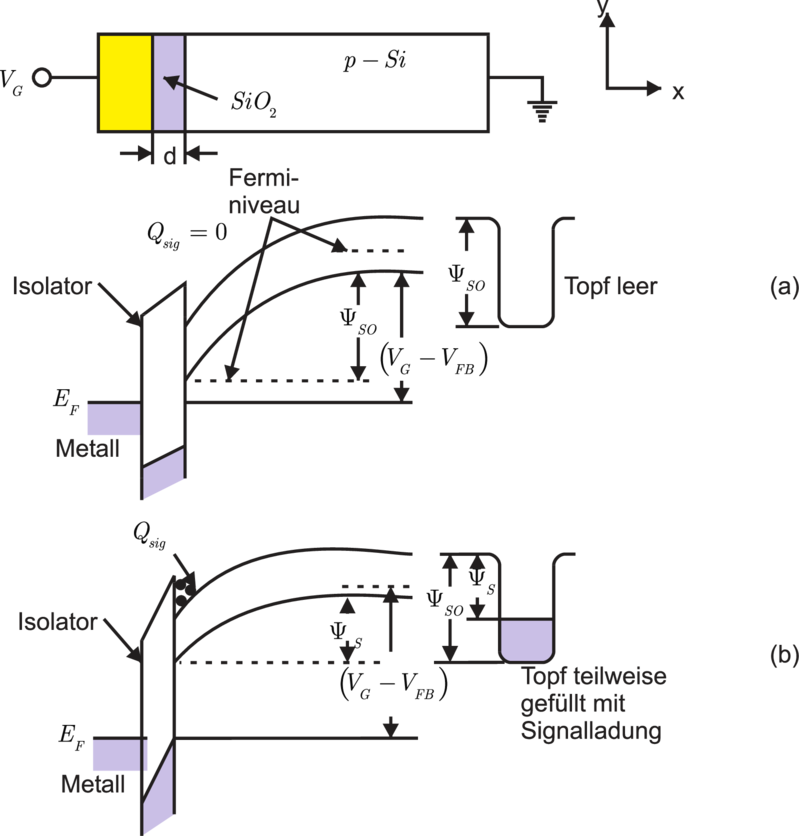

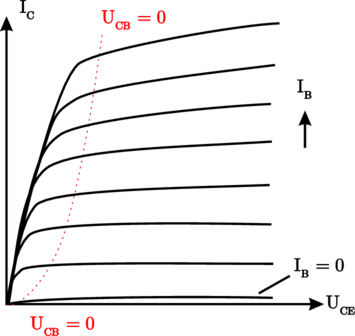

Den Aufbau der Grundeinheit eines Ladungsverschiebelements gibt Abbildung 3.47 wieder. Drei benachbarte MOS–Dioden bilden, abhängig von der Grösse der positiven, angelegten Spannung Potentialtöpfe aus; die Ladung bleibt annähernd im tiefsten Topf erhalten oder fliesst zum tiefsten Topf hin. Das gezeigte Bild gibt eine Drei–Phasen–Verschiebeeinheit wieder.

Setzt man mehrere solche Baugruppen hintereinander (siehe Bild 3.48) und versieht Anfang und Ende der Kette mit einer Eingangs– und Ausgangsschaltung (n–p–Diode und MOS–Gate) ist das Schieberegister komplett.

| Abbildung 3.49.: | Potentialverlauf und Ladungsverteilung im oben abgebildeten CCD–Chip (gezeichnet nach [Sze81]). |

Legt man in geeigneter Weise Spannungen an den Eingang und die MOS–Gates und schliesslich an den Ausgang, funktioniert der Ladungstransport (Abbildung 3.49).

Es gibt verschiedene Elektronenanordnungen und zugehörige Takttechniken (’push–clock–Systeme’): 1–4 Phasensysteme mit Taktfrequenzen von einigen kHz - 100 MHz. 2–Phasensysteme benötigen ‘unsymmetrische’ Gate–Elektroden, 1–Phasensysteme zusätzliche Dotierung.

Die bisher präsentierte CCD–Bauform bezeichnet man als SCCD (surface channel CCD). Ihr Hauptnachteil liegt im Vorhandensein von Trapping–Zentren am Kanalrand. Dies führt zu zusätzlichem Rauschen.

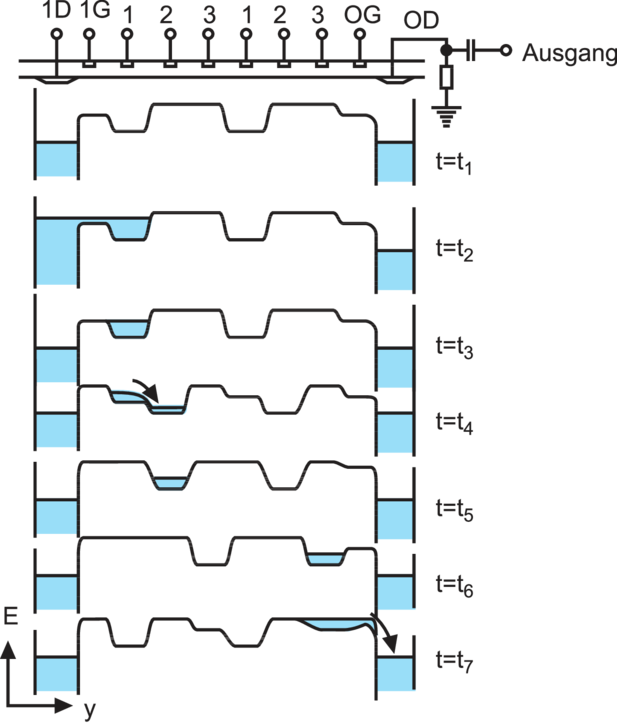

Eine verbesserte Ladungstransfer–Effektivität erhält man mit einem weiteren Grundtyp: BCCD (burried channel CCD). Die ‘vergrabene’ n–Kanalschicht im p–Substrat erhält man durch eine ionenimplantierte n–Schicht auf dem p–Substrat. Streng genommen liegt ein völlig neues Bauelement vor, nämlich ein MO–Kontakt über einem n–p–Kontakt; es handelt sich aber wieder nur um ein unipolares Bauelement.

| Abbildung 3.52.: | Aufbau eines BCCD a). Bändermodell ohne b) bzw. mit c) Signal (gezeichnet nach [Sze81]) |

Im zugehörigen Bändermodell zeigt sich, dass der entstehende n–Kanal nicht mehr direkt an der kritischen Oxid–Halbleiter–Grenzfläche liegt. Das Rauschverhalten dieser Bauelemente ist deutlich besser (Anwendung: hochempfindliche Bildsensoren).

Ein– oder zweidimensionale Bildaufnahmeeinheiten bestehen aus Zeilen oder Arrays von Detektoren, die entweder integrierende Speicher besitzen oder ihre Ladungen ständig an eine Speicherzeile weitergeben müssen. Häufig sind diese Speicher durch eine lichtundurchlässige Schicht geschützt (‘Anti–Blooming’).

Beim eindimensionalen Interline–Konzept wird neben jede Sensorzeile eine CCD-Transportregister–Zeile gesetzt bzw. genauer zwischen zwei Sensorzeilen wird eine Registerzeile gesetzt und die Halbbilder werden abwechselnd ausgelesen in ein sog. CCD–Ausleseregister.

Beim dem in der Abbildung 3.53 dargestellten Frame–Transfer–Konzept wird der gesamte Inhalt eines ganzen Bildbereichs in einem lichtdichten Speicherbereich zeilenweise parallel verschoben. Das Auslesen erfolgt zeilenweise. Zur Erzeugung analoger Videosignale benötigt man einen Videoverstärker, für digitale Kameras geeignete A–D–Wandler und Speicher.

Für informationstechnische Schaltkreise (logische Schaltungen, Speicher) und Leistungsverstärker sind die sog. Transistoren die wichtigsten aktiven Bauelemente. Während die bislang besprochenen Dioden sog. Zweitor–Bauelemente mit zwei äusseren Kontakten sind, kennzeichnet die Transistoren das Vorhandensein von drei Kontakten: sog. Dreitor–Bauelemente. Ströme oder Spannungen zwischen zwei Kontakten werden durch einen dritten Kontakt gesteuert oder ein– und ausgeschaltet.

Es gibt zusätzliche Möglichkeiten zur Klassifizierung von Halbleiter–Bauelementen. Ist für die Funktion des Bauelements nur eine Ladungsträgersorte wesentlich, so spricht man von ’unipolaren’ Bauelementen; sind dagegen beide Ladungsträgertypen wesentlich beteiligt, redet man von ‘bipolaren’ Bauelementen. So auch bei den Transistoren. Abweichend von der Mehrzahl der Autoren stellen wir die Behandlung der Bipolartransistoren noch zurück (schwieriger zu verstehen!). Stattdessen nutzen wir die in Kapitel 3.2.5 und 3.2.6 zuletzt gelegten Grundlagen für das Verständnis der Feldeffekt–Transitoren (FET ‘field effect transistor’) aus.

Im Prinzip sind FETs Widerstände mit zwei Kontakten, die durch eine äussere Spannung an einem dritten Kontakt gesteuert werden. Die Art des dritten Kontakts kann verschieden sein: MESFET und MISFET (Metall–Semiconductor FET und Metall–Isolator–Semiconductor FET). Der Steuerkontakt ist im ersten Fall also ein Schottky–Kontakt, im zweiten Fall ein MIS– oder (in den meisten Fällen in der Praxis) ein MOS–Kontakt.

Der gesteuerte Widerstand besteht aus einem an beiden Enden kontaktierten Stromkanal für die eine, für die Funktion wesentliche Ladungsträgersorte. Es gibt Bauelemente mit einem n–Kanal und hierzu komplementäre mit einem p–Kanal; die letztgenannten Bauelemente sind aufgrund der geringeren Beweglichkeit der Löcher immer langsamer (aber bisweilen einfacher zu fertigen).

Der Kontak am Eingang des leitenden Kanals ist die sog. Source (Quelle), der am Kanalausgang der sog. Drain (wörtlich Abfluss). Der Steuerkontakt trägt die Bezeichnung Gate (Tor). In den FET–Grundformen gibt es ein oder zwei zusammengeschaltete Gates. (Nebenbemerkung: Beim sog. Double Gate FET werden die beiden Gates nicht miteinander verbunden, sondern voneinander unabhängig zur Steuerung des Majoritätsladungsträgerstroms insbesondere für Misch– und Regelschaltungen herangezogen. Nicht zu verwechseln mit dem Thyristor, einem bipolaren Bauelement mit zwei Steuerelektroden.) Kennzeichnend für alle FET–Typen ist die hochohmige Trennung von Steuer–Kontakt und Kanal über eine Verarmungsschicht oder einen Isolator/ein Oxid. Die Eingangswiderstände sind vergleichsweise sehr hoch; die Steuerung erfolgt über die Spannung, die Gateströme sind extrem klein. Die Steuerelektrode (control electrode) ist kapazitiv an die aktive Kanalregion gekoppelt, ein elektrisches Feld kontrolliert die Ladungen in der aktiven Zone und verändert diese, daher der Name ‘Feldeffekt’–Transistor.

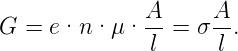

Das Prinzip des FETs besteht also in der Steuerung des Leitwerts eines leitenden Kanals:

| (3.1) |

Man erkennt leicht, dass (bei fester Kanallänge l) entweder der Kanalquerschnitt A oder die Ladungsträgerdichte n zur Steuerung variiert werden muss.

Die Querschnitt–Steuerung nutzen zwei bekannte Transistorklassen. Erstens die sog. Sperrschicht–FET (JFET, Junction FET) und, später hinzugenommen, zweitens die MESFETs. Erstere werden meist in Si, letztere meist in GaAs realisiert.

Die Steuerung der Trägerdichte ist kennzeichnend für die MISFETs und MOSFETs, sowie für die moderne Weiterentwicklung des MESFET, den HEMT (high electron mobility).

Historisch gesehen war der MISFET der erste Transistor, der erdacht worden ist (1939). Im Gegensatz zum Bipolartransistor kommt es bei unipolaren Transistoren nur auf die Majoritätsladungsträger an, d. h. die Anforderungen an das Halbleiter–Material (Reinheit, Kristallinität) sind geringer. Tatsächlich sind unipolare Transistoren in einer grossen Vielzahl von halbleitenden Materialien realisiert worden. Der grosse Nachteil des Vorschlags war aber die technisch äusserst schwierig zu beherrschende Grenzfläche zwischen Isolator und Halbleiter. Der Sperrschicht–FET umgeht dieses Problem: die Steuerung wird weg von der Halbleiter–Oberfläche ins Innere des Halbleiters gelegt. Seine technische Realisierung gelang als erste.

Sperrschicht–FET (JFET)

Die konventionelle Bauform eines JFET kann man sich als ein Stäbchen aus z. B. mässig n–dotiertem Material vorstellen. Die beiden Stirnseiten werden mit ohmschen Kontakten versehen und bilden Source und Drain. Von der Oberseite und von der Unterseite wird stark p–dotiert. Darüber werden die Gatekontakte aufgebracht; diese werden miteinander fest verbunden.

Werden alle Kontakte miteinander verbunden, dann bilden sich jeweils asymmetrische Sperrzonen aus, die wegen der schwächeren Dotierkonzentration hauptsächlich im n–Gebiet liegen. Legt man an die Gates eine negative Spannung an, werden die Sperrzonen breiter und tiefer ins n–Gebiet reichen und sich, bei geeigneter Substratdichte, berühren. Umgekehrt wird eine positive Gate–Spannung den n–Kanal (n–channel) verbreitern. Die Gate–Steuerspannung legt also wie gewünscht die Kanalbreite fest.

Gehen wir nochmals zurück zur Ausgangslage mit verbundenen Kontakten. Wird jetzt einseitig an Drain eine positive Spannung angelegt, beginnt ein Elektronenstrom vom Source–Kontakt zum Drain–Kontakt zu fliessen. Gleichzeitig werden zum positiven Potential hin die Sperrzonen breiter; bei einer bestimmten Drain–Source–Spannung UDS werden sich die Sperrzonen an ihrem Drain–Ende erstmals berühren: die Abschnürspannung Up (pinch–off) ist erreicht. Für UDS < Up werden wir eine lineare Abhängigkeit des Drainstroms ID ∼UDS erwarten, darüber einen fast konstanten Sättigungstrom.

Mit einer negativen Gatespannung UGS < 0 lassen sich die Sperrzonen verbreitern und die Abschnürspannung wird bereits bei kleineren Drainströmen erreicht. Entsprechende Übertragungs– und Ausgangskennlinien sind in Abbildung 3.57 wiedergegeben. Wegen des symmetrischen Aufbaus erhält man die gezeigten Ausgangs–Kennlinien für positive ID bei positiven UDS, und gespiegelt am Ursprung solche für negative ID bei negativen UD; im linearen Kennlinienbereich kann man den JFET als regelbaren Widerstand für Wechselspannungen (symmetrisch zu Null) benutzen. Bei grossen UDS brechen die Drain–Gate–Strecken durch.

Die wichtigsten JFET–Eigenschaften sind:

≈

104 − 106Ω

≈

104 − 106Ω

uDS ≈

…10mA∕V

uDS ≈

…10mA∕V

Den JFET zeichnet eine vergleichsweise sehr lineare, aber kleine Spannungsverstärkung aus, deshalb wird er, wenn auch selten, als linearer Verstärker mit hohem Eingangswiderstand, kleiner Verstärkung und kleinen Rauschzahlen eingesetzt. Wie bei allen FET–Typen sorgt ein negativer Temperaturgradient (ID sinkt, wenn die Temperatur T steigt) für einen homogenen Stromtransport und damit für eine stabile Funktion.

Die statischen Strom–Spannungs–Kennlinien lassen sich nach Shockely (gradual channel approximation model) berechnen, siehe z. B. Roulston[Rou99]. Das Bemerkenswerte daran ist, dass diese Theorie nicht nur auf JFET anwendbar ist, sondern auch auf MESFETs. Beide Male liegt eine Verarmungszone vor, aber im einen Fall ist es die eines p–n–Übergangs, im anderen die eines Schottky–Kontakts. .

Es gibt auch eine planare Aufbauvariante des JFETs (siehe Abbildung 3.58). Auf einem schwach p–dotierten Si–Substrat wird eine n–dotierte Epitaxieschicht aufgewachsen. Für die Kontakte werden stark dotierte n+–Wannen hergestellt, der Steuerkontakt besteht wieder aus einem stark überdotierten p–Bereich und der Metallisierung darüber. Man erhält von oben eine asymmetrische Raumladungszone in den p–Kanal hinein. Von unten wird dieser durch eine asymmetrische Verarmungszone begrenzt, die weit ins p–Substrat reicht. Je negativer die angelegte Gatespannung ist, desto schmaler der Kanal. Legt man wieder eine positive UDS an, so erhält man wieder analog eine asymmetrische Verarmungszone und schliesslich berühren sich die Verarmungszonen wieder, , mit den bekannten Folgen. Eine Diskussion eines p–Kanal–JFET liefe analog.

Die technische Verwirklichung des bereits angesprochenen Double–Gate JFET zeigt gegenüber dem besprochenen Planaraufbau folgende Modifikationen: das Substrat ist kontaktiert und bildet das Gate 2; bei negativer Vorspannung wandert die Sperrzone weiter in die Epischicht; bei angelegter UDS wird sie asymmetrisch.

Auf den ersten Blick gleichen sich die Verhältnisse beim GaAs MESFET sehr. Auf einem intrinsischen oder semi–isolierenden (Cr–dotierten) Material wird zunächst eine undotierte ‘Bufferlayer’ gewachsen, dann folgt die n–dotierte Epischicht; die weiteren Schritte folgen analog. Die Herstellung ist ziemlich einfach.

Der Vorteil besteht einerseits in der hohen Beweglichkeit der Elektronen in GaAs und andererseits sind die Kapazitäten CGS und CGD deutlich kleiner als beim JFET (Seitenwandbeiträge entfallen). Für Mikrowellenanwendungen liegen die kritischen Längen heute unter 200 nm. Die maximale Frequenz steigt wegen fmax = g∕CGate an.

Die Bauelemente zeigen exzellente DC– und HF–Eigenschaften. Sie werden als Subnanosekundenschalter oder als sehr rauscharmer Mikrowellenverstärker eingesetzt. Es gibt sogar integrierte Schaltkreise (MMICs, Monolithic Microwave ICs in Radarsystemen). Da für die III–V–Halbleiter kein brauchbares Oxid zur Verfügung steht, gibt es zum MESFET keine Alternative.

In der Praxis werden die einfach erscheinenden Verhältnisse des idealen Schottky–Kontakts durch die hohe Zahl der Grenzflächenzustände am Metall–Halbleiter–Interface des Gates doch recht kompliziert. Aber wie in Kapitel 3.2.5 schon gezeigt wurde, ändert dies nur etwas am Verständnis, nicht aber an der Funktion der Bauelemente.

Das nebenstehende Bild zeigt neben dem Grundaufbau die zugehörigen elektronischen Bänderschemata. Im intrinsischen GaAs–Substrat liegt EF (nahe) der Energielückenmitte. Im dotierten n–Kanal liegt EF nahe unter der Leitungsbandunterkante. Zum Metall–Halbleiter–Interface hin haben wir die Verarmungszone des Schottky–Kontakts, die positiven Ladungen der ortsfesten Donatoren verursachen Bänderkrümmungen nach oben. Das Fermi–Niveau an der Grenzfläche ist durch die hohe Anzahldichte der Grenzflächenzustände nahe der Mitte des verbotenen Bandes ‘gepinnt’. Der metallene Steuerkontakt ist also hochohmig vom n–Kanal getrennt.

Ohne Vorspannung können auf der niederohmigen Source–Drain–Strecke Elektronen injiziert werden, die im Potentialtopf des n–Kanals, abgesehen von einer leichten Rekombination, sicher transportiert werden können.

Durch Anlegen einer negativen Gatespannung UG wird der Kanal abgeschnürt, indem das Fermi–Niveau des Metalls gegenüber dem des i–GaAs angehoben wird. Da EF an der Grenzfläche gepinnt bleibt, werden die angrenzenden Bänder angehoben, die Verarmungszone wächst nach rechts, der Kanal verarmt an Ladungsträgern und wird schliesslich sperrend.

Die beiden Einträge ‘Auf’ und ‘Zu’ zeigen die Schalterfunktion des Transistors. Neben dem beschriebenen ‘Normal–Auf’–MESFET (normally on), dessen n–Epischicht dicker als die Verarmungsschicht (ca. 50 nm) des Schottky–Kontakts ist, gibt es auch einen ‘Normal–Zu’–MESFET (normally off). Dieser hat eine dünnere n–Epischicht (vergleichbar mit der Schottky–Kontakt–Verarmung) und sperrt deshalb bei UG = 0; für UG > 0 schaltet er auf.

High Electron Mobility Transistor (HEMT) Eine Weiterentwicklung des GaAs–MESFET ist der HEMT. Möglich wurde das durch die Fortschritte in der MBE (Molekularstrahlepitaxie) der III–V–Halbleiter bei der Herstellung von Heterostruktur–MESFETs und durch den gemischten Einsatz von optischen Lithographieverfahren und der Elektronenstrahllithographie zur Bearbeitung kleinster Abmessungen.

Resultat ist ein extrem rauscharmer Transistor für Höchstfrequenzanwendungen. Bei Gatelängen von 50 nm wurden Stromverstärkungs–Abschneidefrequenzen ft von weit über 300 GHz gemessen. Die Anwendung liegt bei Radar– und Satellitenkommunikation.

Der HEMT ist ein Heterostruktur–FET, dessen n–Kanal durch ein 2–dimensionales Elektronengas (2 DEG) an der Grenzfläche zwischen einer AlGaAs/GaAs–Heterostruktur gebildet wird (vergleiche Kapitel 3.2.4). Im ‘Auf’–Zustand (negative Gate–Spannung) können die Potentialtopf–Zustände gefüllt werden, im ‘Zu’–Schaltzustand liegt das Fermi-Energie–Niveau zu tief, der 2 DEG–n–Kanal hat keine Ladungsträger.

MOSFET (Metal Oxid Semiconductor FET)

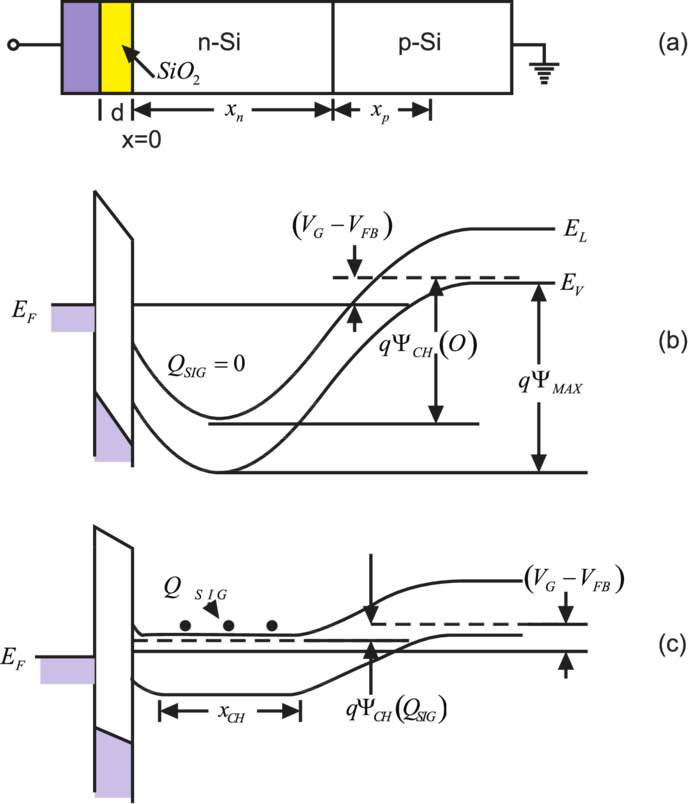

Wiederholt wurde schon darauf hingewiesen, dass MISFETs (oder auch IGFETs, Isolated Gate FETs genannt) praktisch nur auf Si als MOSFET realisiert werden. Wie schon in Kapitel 3.2.6, kann man am MIS–Kontakt, abhängig von der Substrat–Dotierung und der angelegten Spannung an der Grenzfläche Anreicherung oder Verarmung der Majoritätsladungsträger erreichen (oder gar Inversion der Minoritätsladungsträger; letztere spielte beim CCD–Element die entscheidende Rolle). Beim JFET war nur der Verarmungsbetrieb möglich, beim MISFET kommt die Möglichkeit des Anreicherungsbetriebs hinzu. Prinzipiell sind n– und p–Kanäle denkbar. Aber da Grenzschichtladungen meist positiv sind, entspricht dies einer Vorspannung am Gate und es gibt deshalb eine Tendenz zum n–Kanal (Verarmung im p–Material, Anreicherung im n–Material).

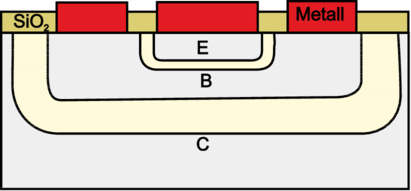

Beim MOSFET kontrolliert das elektrische Feld (Gatespannung gegen Kanalpotential) über das Oxid die Ladungsträgerdichte und damit den Kanalwiderstand. Der Eingangswiderstand ist extrem hoch (1012 −1016Ω). Der abgebildete MOSFET–Aufbau gibt einen n–Kanal–MOSFET wieder: Ausgangsmaterial ist ein mässig p–dotierter Si–Wafer. Die beiden Source– und Draingebiete sind durch Ionenimplantation hoch n–dotiert worden; darauf befindet sich hoch n–dotiertes Poly–Silizium für die Kontaktierung.

Bei Gatespannung UG = 0 befindet sich (die Grenzflächenladungen seien hier vernachlässigt) p–Si unterm Gate. Liegt eine Spannung USD an, ist ein p–n–Übergang gesperrt, der Strom ID ist nahezu Null; der Transistor ist im ‘Zu’–Zustand.

Machen wir jetzt das Gate positiver als die Source (UGS > 0), so erhät man durch Inversion (Ei < EF) eine starke n–Anreicherungsschicht nahe der Grenzschicht. Dieser n–Kanal verbindet die Source– und Gate–Wannengebiete leitend. Eine positive Gatespannung macht den n–Kanal–MOSFET ‘auf’.

Bei invertierter Dotierung erhält man einen p–Kanal–MOSFET in einem n–Si–Substrat. Bei Gatespannung Null ist dieser Typ im ‘Zu’–Zustand, aber bei negativer Gatespannung (invertierter Spannung) ist auch hier der ‘Auf’–Zustand erreicht.

In Abbildung 3.64 sind die Ausgangskennlinien zweier n–Kanal–MOSFET–Typen zum Vergleich wiedergegeben. Auch hier zeigt die kleinere Kanallänge die besseren Eigenschaften, nämlich hier den höheren Ausgangsstrom. Aber aufgrund der kleineren Gatekapazität ist auch die Grenzfrequenz höher, das Schaltverhalten schneller.

Die Anwendung der MOSFETs nutzt die sehr guten dynamischen Eigenschaften dieser Bauelemente in HF–Verstärkern und zu Schaltzwecken. (Über die Verwendung in der Verstärkerintegration wird noch zu reden sein.) Grösster Nachteil der MOSFETs ist die maximal verträgliche Gatespannung von 50 - 100 V; elektrostatische Ladungen liegen im Alltag häufig 100 mal höher.

MOSFETs eignen sich zur Herstellung hochintegrierter Digitalschaltungen besser als Bipolartransistoren; sie benötigen weniger Fläche auf dem Si–Wafer und sind deshalb preisgünstiger. Bis Mitte der achziger Jahre wurden die Schaltungen in NMOS–Technologie ausgeführt. Mit dem 1 Mb–DRAM–Speichern (1 Megabit Dynamic Random Access Memory) wechselten die Hersteller zur deutlich komplexeren CMOS–Technologie; die kleinsten Strukturgrössen betrugen MFS = 1, 2μm (Minimal feasable size).

Durch die Herstellung von n–Kanal und p–Kanal Anreicherungs–MOSFETS nebeneinander auf einem Substrat ist deren Verschaltung zu einem Inverter mit besonderen Eigenschaften möglich: er schaltet schnell; seine Übertragungskennlinie zeigt einen steilen Wechsel, am Ausgang liegt entweder die volle Versorgungsspannung V DD oder die Null an. In den stationären Zuständen fliesst kein Strom; der Ruhestrom ist Null, nur beim Schalten wird Leistung verbraucht. Bei hohen Taktraten und häufigem Schalten relativiert sich zwar dieser Vorteil, aber die CMOS–Technik hat noch weitere: vereinfachtes logisches Design, kleine Anzahl von Transistoren in den peripheren Hilfs–Schaltkreisen (support circuits) (der sog. Speicherwirkungsgrad wird > 50%), kleinere Rauschempfindlichkeit.

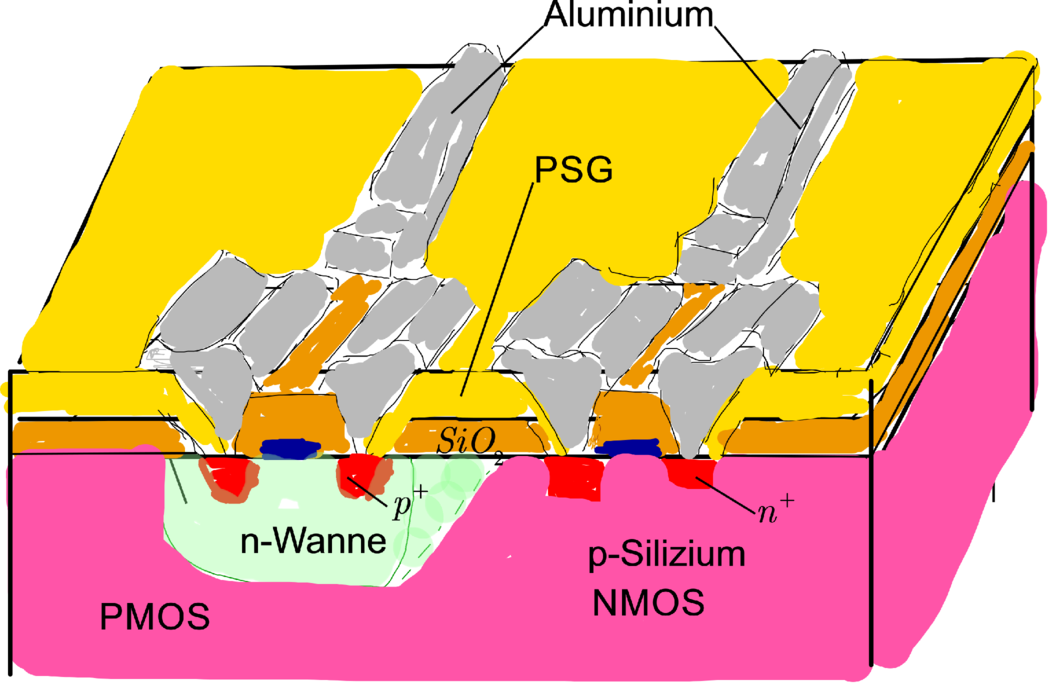

Heute beträgt der Marktanteil der CMOS–Technologie über 75 %; ca. 10 % dieser Bauelemente sind analoge Schaltungen. Das Bild unten gibt als technologisches Beispiel das Schaltbild und den schematischen Aufbau eines CMOS–Inverters auf n–Substrat wieder. Dabei sind n–MOSFET und p–MOSFET zueinander ‘komplementär’: CMOS (Complementary MOS).

Aus zwei Invertierern lässt sich ein einfaches Flip–Flop aufbauen, eine Schaltung mit zwei stabilen, eindeutig unterscheidbaren Schaltzuständen. Fügt man noch zwei weitere MOS–Transistoren hinzu, dann erhält man die Zelle eines SRAM–Speichers (Static RAM), eines sehr wichtigen Halbleiterspeichers also, siehe später.

Am Beispiel der technologischen Entwicklung des Inverters lässt sich die historische Entwicklung der Halbleiter–Technologie demonstrieren: Den einfachsten Invertierer kann man aus einem Ladewiderstand und einem PMOS–Transistor herstellen. Integrierte Planarwiderstände benötigen aber eine grosse Fläche. Viel platzsparender ist es, Source und Gate zu verbinden und so einen Widerstand zu realisieren. Die entsprechede Technologie heisst ‘PMOS Aluminium–Gate–Prozess’. Es handelt sich um eine sog. Einkanal MOS–Technik auf einem n–Silizium–Substrat, bei der es nur selbstsperrende p–Kanal–MOSFETs (enhancement type E) gibt. Diese Technik benötigt nur vier verschiedene Masken und eine Metallisierungs–Schicht.

Eine Voraussetzung für diese Technik ist das Vorhandensein ausgeklügelter Lithographietechniken. Bis heute verwendet man in der Chipfertigung optische Lithographietechniken, um in aufgeschleuderten, photoempfindlichen Polymerlacken laterale Strukturen lokal zu öffnen, durch die additiv oder subtraktiv die Waferoberfläche oder oberflächennahe Si–Schichten gezielt verändert werden können (Oxidieren, Ätzen, Dotieren). Schritt für Schritt können so hochkomplexe Planar–Schaltungen aufgebaut werden. Die kleinste Strukturgrösse betrug anfangs 4 −10μm. Schneller wurden die Inverter durch die Einführung des ‘NMOS Aluminium–Gate–Prozesses’ auf p–Substrat.

Eine merkliche Verbesserung erzielte man aber erst mit der Einführung der ‘n–Kanal Aluminium–Gate MOS–Technik’. Die Ladewiderstände werden hier durch selbstleitende NMOSFETs gebildet (depletion type D), die Schalttransistoren sind wieder vom E–Typ: sog. E/D–Inverter. Der Preis für die Verbesserung sind zwei zusätzliche Masken– und ein zusätzlicher As–Implantations–Dotierschritt zur Einstellung der Schwellenspannung des D–Typ–FETs.

Die ursprüngliche Technik erfuhr im Laufe weniger Jahre zahlreiche Verbesserungen. Die wichtigste war wohl der Übergang zur ‘NMOS Silizium–Gate Technologie’. Dabei wird Aluminium als Material zur Gate–Kontaktierung ersetzt durch polykristallines Silizium, das durch nachträgliche Dotierung leitfähiger gemacht werden kann (‘Polysilizium’, durch LPCVD–Abscheidung). Dies geschieht gleichzeitig mit der Source/Drain–Implantation, d. h. man benötigt hierfür keine spezielle Maske mehr, dieser Implantationsschritt ist ‘selbstjustierend’. Zusätzlich verkleinern sich die störenden Überlappungskapazitäten (‘Miller capacities’) zwischen Gate und p–dotierten Source/Drain–Kanälen.

Weitere Schritte sind vergrabene n+–dotierte Si–Leiterbahnen und eine weitere selbstjustierende Oxidationstechnik, die LOCOS–Technik (Local Oxidation of Silicon), die zusätzlich Abscheide– und Ätztechniken für das hierbei benötigte Si3N4 erfordert. Überhaupt werden die eingesetzten Materialien immer zahlreicher und raffinierter; etwa Silizide zur Kontaktierung, Nitride als Diffusionsbarrieren, Mischoxide, Gläser und AlSiCu–Legierung bzw. seit neuestem Cu (als Leiterbahnenmaterial in bis zu vier Metallisierungsebenen).

Zunächst aber erzwang die in den hochintegrierten Bauelementen mit der Verkleinerung der Strukturgrössen und der Steigerung der zu einer Schaltung gehörenden Transistoranzahl über die Jahre angestiegene Verlustleistung den Wechsel zur CMOS–Technologie. Der zugehörige Inverter wurde bereits eingangs besprochen.

Das Endprodukt des ‘n–Wannen Silizium–Gate CMOS–Prozesses’ gibt die Abbildung 3.67 wieder. Auf einem mässig p–dotierten (100)–Substrat wurde rechts der NMOS–FET direkt hergestellt, links dagegen wurde eine mehrere μm tiefe ‘Wanne’ (engl. well) mit Phosphor n–dotiert, um darauf durch p+–Implantation den PMOSFET zu bauen. Die Schaltungsdesigner bemühen sich, möglichst nicht nur einzelne, sondern immer mehrere p–Kanal–Transferelemente in eine grosse n–Wanne zu plazieren, was die Funktionssicherheit im späteren Betrieb erhöht.

| Abbildung 3.67.: | CMOS: p– und n–Kanal–E–Type MOSFETs, schematisch (skizziert nach Hilleringmann [Hil96]). |

Reale CMOS–ICs herzustellen erfordert heute etwa 25 Masken. Enthalten die Schaltungen (wie bei den DRAMs) noch aufwendige MOS–Kondensatoren, so steigt die Maskenanzahl auf 30 bis 35 an. (Zum Vergleich: für eine moderne Laserdiode benötigt man nur 5 verschiedene Masken.)

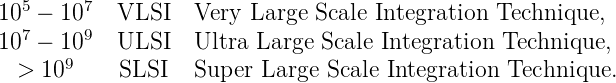

Die produzierten Schaltungen enthalten immer mehr Transistoren:

Hierzu werden die Schaltungslayouts nicht nur von Speichergeneration zu Generation ‘geshrinkt’, sondern dreidimensionaler. Die MOSFET–Zelle wird dabei mit dem Skalierungsfaktor α verkleinert, z. B. α = 0, 7. Dann erhöht sich die Schaltgeschwindigkeit mit 1∕α, die Schaltungsdichte ∼ 1∕α2, der Leistungsverbrauch pro Inverter sinkt ∼α2, die Verlustleistungsdichte bleibt annähernd konstant.

Die aktuelle Leiterbahnbreite liegt bei 110 −130nm in der Spitzentechnologie. Die nächsten Stützpunkte (nodes) in der technischen Entwicklung werden, siehe den Skalierungsfaktor α, sein: 100 nm (im Jahre 2005/6), 70 nm, 50 nm (im Jahre 2011/12) und 35 nm (2014 oder früher). Ein Ende jeglicher CMOS–Technologie wird bei 20-30 nm erwartet. Die Generationswechsel erfolgen gemäss dem ‘Mooreschen Gesetz’ etwa alle ≲ 3 Jahre, siehe NTRS (National Roadmap for Semiconductors) der SIA (Semiconductor Industry Association) der USA bzw. seit 1999 die ITRS (International Technology Industry Association) aller Industriestaaten. Diese ‘road maps’ wagen jeweils eine 15 Jahre–Prognose für die künftige technologische Entwicklung in der Halbleiterindustrie, an der sich die Produzenten und Zulieferer orientieren können.

Eine der spannendsten Fragen des Jahres 2001 wird sein, mit welchem Lithographieverfahren die Industrie die 100 nm–Technologie angehen wird. Excimer–Laser gestützte ‘optische’ Lithographieverfahren haben überraschenderweise auch hier sehr grosse Chancen. Allerdings wird das Problem der immer kleiner werdenden Tiefenschärfe immer gravierender; die Topographie einer CMOS–Schaltung muss deshalb auch nach vielen Prozessschritten noch sehr plan bleiben, will heissen < 1∕2μm. Aus diesem Grund werden bereits heute planarisierende Polierschritte (CMP Chemomechanical Polishing) in die Prozessfolge eingefügt, was exzessive Reinigungsschritte mit sich zieht. Für die nachfolgenden Technologiegenerationen stehen Projektionsverfahren mit Elektronen und Ionen optional zur Verfügung, ebenso Photonen des EUV (Extreme Ultraviolet bei 13,5 nm Wellenlänge). Dabei ist die Wechselwirkung zwischen Ionen und Resist die für die Auflösung günstigste. Dagegen wird die Röntgenstrahl–Lithographie als Schattenwurfverfahren nur ein wichtiges Spezialverfahren in der Mikromechanik zur Belichtung sehr dicker Resists (mehrere mm) mit ≤ μm Auflösung bleiben.

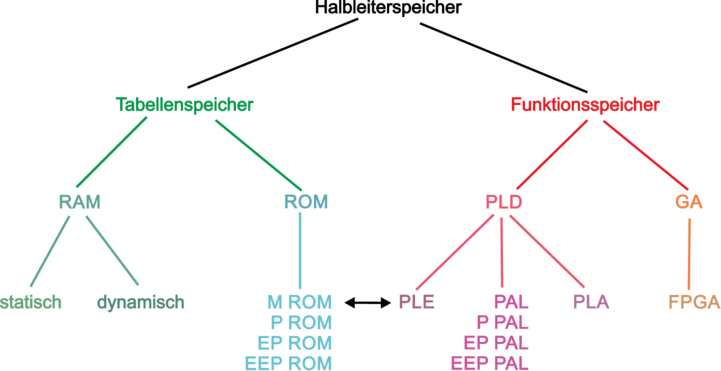

Das wichtigste Marktsegment neben den Mikroprozessoren ist das der digitalen Halbleiter–Speicher. Die Abbildung 3.68 gibt einen Überblick über die gängigen Bauelement–Typen.

| RAM | = | Random Access Memory | PLD | = | Programmable Logic Device |

| ROM | = | Read Only Memory | PLA | = | Programmable Logic Array |

| M | = | Masken-programmiert | PAL | = | Programmable Array Logic |

| P | = | Programmierbar | PLE | = | Programmable Logic Element |

| EP | = | Löschbar und programmierbar | GA | = | Gate Array |

| EEP | = | Elektrisch löschbar | FPGA | = | Field Programmable GA |

| und programmierbar |

| Abbildung 3.68.: | Übersicht über die verbreitesten Halbleiter–Speichertypen (adaptiert aus Tietze/Schenk [TS99]). |

Im Folgenden sollen die Schaltungszellen der wichtigsten

Tabellenspeicher jeweils kurz diskutiert werden.

In Tabellenspeichern legt man ‘wortweise’ den Inhalt von

beliebigen Tabellen (z. B. Computerprogramm, Messwerte)

ab. Jedes Wort hat seine eigene Adresse; bei RAMs (Random

Access Memory) und ROMs (Read Only Memory) kann, im

Gegensatz zu Schieberegistern, jederzeit auf jede Adresse

zugegriffen werden (‘wahlfreier Zugriff’). RAMs werden im

Normalbetrieb beschrieben und gelesen; beim Abschalten

der Betriebsspannung verlieren sie ihren Speicherinhalt

(flüchtiger Speicher, volatile memory). ROMs sind im

Normalbetrieb nur auslesbare Festwertspeicher. Je nach Typ

sind sie ein– oder wenige Male beschreibbar; sie behalten

aber auch ohne Versorgungsspannung sehr lange ihren

Inhalt (nicht flüchtiger Speicher, non-volatile memory).

Statische RAMs (SRAMs) sind wie DRAMs bit– und wortweise organisiert, benötigen also Hilfsschaltkreise wie Adressdecoder (Spalten– und Zeilen–Decoder), Ein– und Ausleseverstärker, Zwischenspeicher (adress–latch), etc. Die Speicher–Matrix besteht aus Flip–Flop–Speichern. In Abbildung 3.69 sieht man eine Flip–Flop–Speicherzelle in CMOS–Technik, die sog. statische Sechs–Transistor–Zelle. Es handelt sich um ein kreuzgekoppeltes Flip–Flop in Komplementärkanal–Technik (T1, T3 und T2, T4). Zum Ändern der stabilen Zustände werden die n–Kanal–E–Typ–MOSFETs T5 und T6 benötigt. Zum Schreiben werden kurzzeitig die Schalter Sw und Ss oder Ss geschlossen, zum Lesen nur Sw. Nach dem Einschalten befinden sich die Flip–Flops statisch in den Zuständen 0 oder 1 und können sofort beschrieben werden.

| Abbildung 3.70.: | DRAM–Zelle, von links: Schaltbild, schematischer Aufbau der 1 Mb– und einer 4 Mb–Zelle mit Grabenkondensator (skizziert nach Hinsch [Hin96]). |

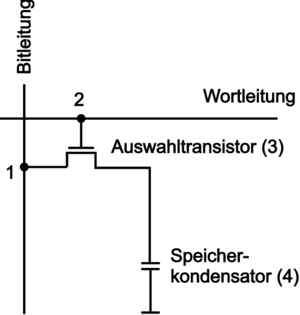

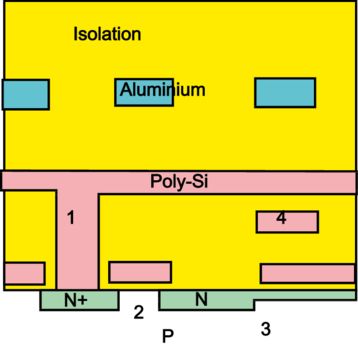

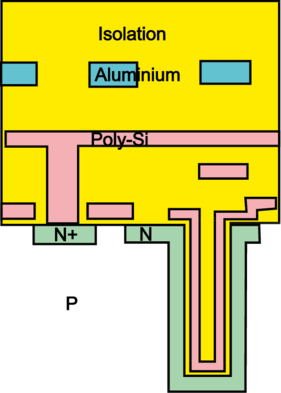

Dynamische RAMs (DRAMs) haben ungefähr die vierfache Speicherkapazität vergleichbarer SRAMs. Ihre Speicherzelle besteht nur aus einem Auswahltransistor (Schalter) und einem MOS–Kondensator (Speicherkapazität CS). Die Source des selbstsperrenden NMOS–Transistors ist mit der Bitleitung (Datenleitung mit der Leitungskapazität Cb) verbunden, das Gate mit der Wortleitung. Schliesst man — über eine positive Spannung am Gate — den Schalter, fliessen Ladungen von oder zur Bitleitung; der Kondensator wird ent– oder aufgeladen. Den Speicherkondensator bilden die flächig erweiterte Drain und, isoliert über ein hochwertiges Oxid (d < 150nm), die Gegenelektrode aus Metall oder heute üblicherweise aus Polysilizium. (Im Bild: 1 = Bitleitung über der Source, 2 = Wortleitungsende als Gate über dem n–Kanal, 3 = Drain mit planarer Erweiterung (storage node), 4 = flächige Topelektrode (cell plate), darüber im isolierenden Oxid eine Wortleitung einer nebenliegenden Speicherzelle.)

Beim Lesen wird die Kondensatorspannung registriert und gleichzeitig die Ladung verändert (destruktives Lesen). Das Vorhandensein von Ladung entspricht der logischen ‘1’ und diese wird beim Lesen verkleinert, da die Datenleitung auf niedrigerem Potential liegt, umgekehrt liegt die Datenleitung aber auf höherem Potential als der leere Kondensator, der die logische ‘0’ repräsentiert. Das beim Ladungstransfer erzeugte Signal ΔV b ist sehr klein, typisch 100 - 200 mV, denn die Kapazität der Datenleitung und unvermeidbare Streukapazitäten sind mehr als zehn Mal grösser als die Speicherkapazität, die man ja der Fläche wegen klein halten will. Näherungsweise gilt:

| (3.2) |

Weil bei jedem Technologiegenerationswechsel sowohl die interne Versorgungsspannung V DD als auch Cb um den selben Faktor d verkleinert werden, muss CS ≳ 25 − 50fF pro Zelle konstant bleiben. Die empfindlichen Schreib–Lese–Verstärker sind praktisch nicht mehr verbesserbar. Jedes (wortweise) Lesen erfordert als ein (wortweises) Neuschreiben der Speicherinhalte (Refresh).

Unvermeidbar sind die Source–Drain–Leckströme des Schalttransistors, d. h. die Kondensatorladung ändert sich immer. Deshalb müssen alle Speicherzellen periodisch ‘aufgefrischt’ werden (Refresh Zyklen). Die Haltezeit einer Zelle beträgt typischerweise 1 – einige 100 ms; bei DRAMs mit 60 ns Zugriffszeiten erfolgt das Auffrischen in 16 μs alle 8 ms. Die Refresh–Schaltungen beanspruchen einen erheblichen Flächenanteil.

Die Kapazität des planaren Speicherkondensators ist mit

CS =  = 𝜖0·𝜖r·

= 𝜖0·𝜖r· gegeben. Bei einer internen Spannung von

2,5 V und bei Verwendung des gewohnten SiO2 macht es die

Durchschlagfestigkeit des Oxids (7 MV/cm, eigentlich 5

MV/cm) nötig, dass ein 30 fF–Kondensator eine Fläche von

rund 3μm2 benötigt. Für ein 4 Mb–DRAM war dieser

Flächenbedarf bereits zu gross. Die Auswege sind:

gegeben. Bei einer internen Spannung von

2,5 V und bei Verwendung des gewohnten SiO2 macht es die

Durchschlagfestigkeit des Oxids (7 MV/cm, eigentlich 5

MV/cm) nötig, dass ein 30 fF–Kondensator eine Fläche von

rund 3μm2 benötigt. Für ein 4 Mb–DRAM war dieser

Flächenbedarf bereits zu gross. Die Auswege sind:

Gerade der Übergang zum vergrabenen Kondensator hat die Integrationsdichte in den letzten Jahren stärker erhöht, als es nach den ‘Roadmaps’ zu erwarten war. Diese Technik stellt grösste Anforderungen sowohl an die isotrope Nassätztechniken als auch an die anisotropen Plasmaätztechniken. Das Ätzen eines merere μm tiefen, verrundeten Zylinderlochs, die Abscheidung eines geschlossenen, hochwertigen Oxids und das Einfüllen der Deckelelektrode sind äusserst komplexe Verfahrensschritte. Die selben Techniken werden in STI (Shallow Trench Isolation) –Prozess zur elektrischen Trennung von vergrabenen Leitungen verwendet. Die Kombination von Oxid– und Trench–Isolation kennzeichnet heute die ‘Advanced CMOS–Techniques’. Obwohl die Stapelkondensatoren weit grössere Möglichkeiten in der Wahl des Isolators zulassen, führt die mit ihrer Herstellung verbundene Aufrauhung der Chipoberfläche in der gegenwärtigen Lithographietechnik zu grossen Problemen.

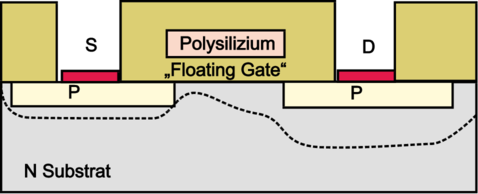

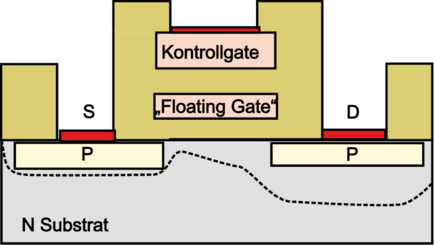

Abschliessend einige Bemerkungen zu den nichtflüchtigen Festwertspeichern. Sie basieren ebenfalls auf MOS–Strukturen. Die früher üblichen PROM–Bausteine (Programmable ROM) mit ihren Schmelzsicherungen für jedes Bit sind heute nicht mehr üblich. An ihre Stelle sind die EPROMs (Erasable PROM) getreten. Die ursprüngliche MOS–Struktur verwendet ein ‘Floating Gate’, das von einem etwa 100 nm dicken Oxid vom Silizium isoliert ist und so praktisch keine Leckströme zulässt. Legt man beim Schreiben zwischen Source und Drain eine ca. 20 V hohe Spannung an, so gelangen via ‘avalanche injection’ heisse Elektronen auf die Gateelektrode, wo sie wenigstens 10 Jahre als Ladung erhalten bleiben. Vorhandene Ladungen schalten die Source–Drain–Strecke bleibend durch, nicht vorhandene Gateladung sperrt. Mit einer ca. zwanzigminütigen UV–Lichtbestrahlung ist der EPROM–Speicher löschbar.

| Abbildung 3.71.: | FAMOS–Struktur des EPROMs und SAMOS–Struktur des EEPROMs (skizziert nach Roulston [Rou99]). |

Eine verbesserte Struktur ist die SAMOS (stacked gate), die eine zweite, floatende Gate–Elektrode als Auswahl–Elektrode vorsieht. Zum Schreiben wird hier zusätzlich auf das Auswahlgate eine positive Spannung gelegt.

Eine SAMOS–Struktur verwendet auch das EEPROM (Electrically Erasable PROM). Zum Löschen wird eine positive Spannung ans Kontrollgate gelegt, alle anderen Kontakte auf Null; die Elektronen tunneln dann von der Floating–Gate–Speicherelektrode zum Kontrollgate. Modifizierte SAMOS–Strukturen haben z. B. verringerte Abstände zu einem erweiterten Draingebiet und Löschen durch Elektronentunneln vom Floating–Gate zum Drainkontakt. Die Anzahl der Schreib/Löschzyklen ist auf ca. 104 begrenzt.

Nebenbemerkung: Eine modifizierte FAMOS–Struktur verwenden die sog. Flash–Speicher, die dadurch ebenfalls elektrisch löschbar sind. Ihr Oxid ist lokal dünner und erfordert ein extremes Mass an Perfektion für ca. 106 Schreib/Löschzyklen.

Zwei gegeneinander geschaltete p–n–Übergänge bilden einen Bipolartransistor. Es gibt zwei Reihungsmöglichkeiten: npn und pnp. Im gebräuchlichen Fall des npn–Transistors tragen Elektronen den für das Bauelement bestimmenden Strom, im Falle des pnp–Transistors sind es Löcher. Die drei Dotierbereiche sind jeweils ohmsch kontaktiert; die Anschlüsse werden immer ‘Emitter’, ‘Basis’ und ‘Kollektor’ genannt.

Die Bezeichnung bipolar rührt von dem Fakt her, dass in jedem Dotiergebiet Majoritäts– und Minoritätsladungsträger für die Bauelementefunktion wesentlich sein können; der Begriff ‘Injektion’ im Zweitnamen weist darauf hin, dass vom Emittergebiet Majoritätsladungsträger in das Basisgebiet injiziert werden, wo sie Minoritätsladungsträger weit ab vom thermodynamischen Gleichgewicht sind. Der Emitter–Basis–Übergang wird im Durchlass–, der Basis–Kollektor–Übergang stets in Sperrrichtung betrieben. Die relevanten Ausdehnungen aller Dotiergebiete sind (100 - 1000 mal) kleiner als die Diffusionslängen der Ladungsträger, d. h. die Kontaktzonen beeinflussen einander stark.

Verglichen mit den unipolaren Transistoren, die i. allg. schnell, rauscharm und temperaturstabil gebaut werden können, sind bipolare Transistoren in geeigneten Beschaltungen vor allem hervorragende Leistungsverstärker. Man begegnet ihnen häufig als Einzelelement; in der Höchstintegration spielen sie zahlenmässig eine untergeordnete Rolle.

n–p–n–Bipolartransistoren

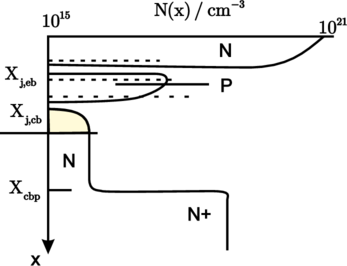

Abbildung 3.73 zeigt den prinzipiellen eindimensionalen

Aufbau dieses Bauelements in sog. Basisschaltung, d. h. der

Basiskontakt liegt auf Masse. Der EB–Kontakt ist mit

UBE ≈−0, 7V leitend gesteuert, UBC wählt man so hoch

(z. B. = ±5V), dass auch bei grösserem Lastwiderstand der

BC–Kontakt kräftig gesperrt wird. Die Dotierkonzentrationen

sind sehr ungleich und die Übergänge abrupt. Das Emittergebiet

ist stark n+ dotiert, die Basis ist beim klassischen Transistor

homogen und deutlich niedriger p dotiert, der Kollektor

nochmals deutlich niedriger n dotiert. Die Basisschicht

ist sehr dünn, das Kollektorgebiet vergleichsweise weit.

Die Raumladungszonen sind asymmetrisch; die der

Injektionsdiode sehr schmal und niederohmig, die der

gesperrten Diode sehr breit und tief im Kollektorgebiet, ihre

zugehörige Kapazität sehr klein, ihr Widerstand hoch.

Das elektronische Bänderschema (Abbildung 3.74) gibt — gestrichelt — die Verhältnisse ohne Vorspannungen im thermodynamischen Gleichgewicht wieder und — durchgezogen — die des Normalbetriebs. Von links diffundieren Elektronen InE durch die schmale Sperrzone; je grösser NE, desto mehr. Gegenüber dem thermischen Gleichgewicht nB0 ist am emitterseitigen Basisrand die Minoritätsladungsrägerdichte nB erhöht gemäss

![nB (0) = nB0 exp [UBE ∕kBT ].](phys_elektr665x.png) | (3.3) |

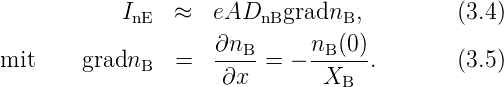

Der Emitterstrom teilt sich in der Basis auf. Der Grossteil der Elektronen (≥ 99%) wird vom elektrischen Feld des gesperrten B–C–Kontakts in den Kollektor abgesaugt: InC. Der kleine Rest (≤ 1%) rekombiniert mit den an der Basis injizierten Löchern. (Diese Stromverteilung ist eine Ursache des vergleichsweise vergrösserten Rauschens.) Näherungsweise gilt also InE ≈InC, solange die Basislänge deutlich kleiner als die Diffusionslänge Ln ist.

Nebenbemerkung:

Das Eindiffundieren der Elektronen in die Basis limitiert das

zeitliche Verhalten des klassischen Bipolartransistors

durch Laufzeiteffekte. Moderne Varianten sind durch

ein inhomogenes Basisdotierprofil gekennzeichnet; das

damit verbundene elektrische Feld beschleunigt die

Ladungsträger zum Kollektor hin: ‘Drifttransistoren’ statt

‘Diffusionstransistoren’. (Diese erreichen Transitfrequenzen

von einigen GHz.)

Die Verteilung der Minoritätsladungsträger in der Basis ist

gegenüber der einer blossen Diode (exp ![[− x∕Ln ]](phys_elektr666x.png) ) stark

verändert; die Anzahldichte fällt aufgrund der Sogwirkung des

gesperrten BC–Kontakts (∼ exp

) stark

verändert; die Anzahldichte fällt aufgrund der Sogwirkung des

gesperrten BC–Kontakts (∼ exp ![[− x∕xB ]](phys_elektr667x.png) ) praktisch am

kollektorseitigen Rand der Basis (bei xB: abhängig von

UBC) auf Null. Oberhalb des thermischen Gleichgewichts,

zum Emitter hin, überwiegt die bereits oben eingeführte

Rekombination, zum rechten Rand der Basis hin ist

nB < nB0, d. h. hier liegt eine schwache Generation von

Minoritätsladugsträgern vor. Für den Elektronenstrom gilt:

) praktisch am

kollektorseitigen Rand der Basis (bei xB: abhängig von

UBC) auf Null. Oberhalb des thermischen Gleichgewichts,

zum Emitter hin, überwiegt die bereits oben eingeführte

Rekombination, zum rechten Rand der Basis hin ist

nB < nB0, d. h. hier liegt eine schwache Generation von

Minoritätsladugsträgern vor. Für den Elektronenstrom gilt:

![InE ≈ eADnBnB0--exp [eUBE ∕kBT ] ≈ InC.

xB](phys_elektr669x.png) | (3.6) |

Die Minoritätsladungsträgerdichte im Kollektor ist zum Basisrand hin aufgrund des Löchergenerationsstroms IG ebenfalls auf nahezu Null reduziert. Ein zweiter Leckstrom besitzt noch mehr Relevanz. Die in die Basis injizierten Löcher können in der Basis, im EB–Sperrgebiet oder aber erst im Emittergebiet rekombinieren: IR. Dieser Löcherstrom wächst mit der Majoritätsladunsgträgeranzahldichte, also mit der p–Dotierkonzentration der Basis. Die Basis kann deshalb nicht beliebig niederohmig gemacht werden, die eindiffundierenden Löcher und die damit verbundene Kapazität limitieren das Schalt–/Zeitverhalten aller Bipolartransistorvarianten. (Eine kleine Löcherdiffusionslänge LpE wäre hilfreich.)

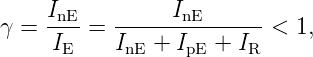

Ein Mass für die Leistungsfähigkeit des Transistors ist das Verhältnis zwischen dem Majoritätsladungsträgerstrom, der die Emittergrenze erreicht und dem Anteil, der im Emitter durch Rekombination verloren geht (Emitterwirkungsgrad). Häufig angegeben wird die sog. Emittereffizienz γ:

| (3.7) |

da IpE und IR entgegengesetztes Vorzeichen besitzen. Die klassische Bipolartransistoren–Theorie liefert die Aussage, dass für eine hohe Effizienz das Produkt DnB·nB0 möglichst gross sein soll und deshalb wird das Emittergebiet sehr hoch dotiert.

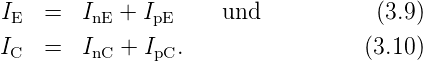

Für die technischen Ströme gilt der Zusammenhang:

Die erwähnte ‘klassische’ Theorie liefert schliesslich für die Übertragungskennlinie IC(UBE) näherungsweise den Zusammenhang:

![eADnBnB0

IE ≈ ----------exp [eUBE ∕kBT − 1] ≈ IC,

Ln](phys_elektr674x.png) | (3.12) |

d. h. wir haben eine typische Diodenkennlinie vorliegen, deren ‘Vorwärtsstrom’ IC wieder bei UBE ≳ 0, 6V merklich einsetzt.

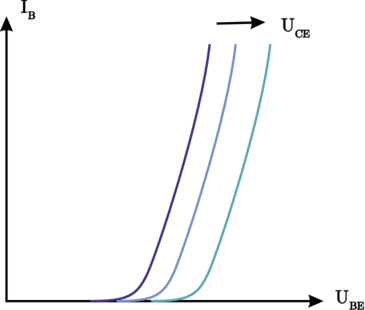

Die sog. Steilheit (small–signal transconductance)

gm =  ist eine weitere Grösse zur Charakterisierung, siehe

Abbildung 3.75 (Einfluss einer Steuerspannungsänderung auf

den Ausgangsstrom). Die Ausgangskennlinien zeigen die

Sperrströme der BC–Diode, die Höhe des Sperrstromes wird

durch UBE bzw. IB gesteuert.

ist eine weitere Grösse zur Charakterisierung, siehe

Abbildung 3.75 (Einfluss einer Steuerspannungsänderung auf

den Ausgangsstrom). Die Ausgangskennlinien zeigen die

Sperrströme der BC–Diode, die Höhe des Sperrstromes wird

durch UBE bzw. IB gesteuert.

Es gibt drei verschiedene Grundschaltungen; der Kontakt, der auf Erdpotential gelegt wird, gibt der Schaltung ihren Namen: Basis–, Emitter– und Kollektorschaltung.

Die Basisschaltung ist gekennzeichnet durch einen niederohmigen Eingang, einen hochohmigen Ausgang; ihre Stromverstärkung ist ≲ 1, eine Spannungsverstärkung und damit Leistungsverstärkung ist möglich.

Die gebräuchlichste Grundschaltung ist die Emitterschaltung. Der Emitteranschlusss liegt auf Masse, die Spannungsversorgung des Transistors erfolgt über einen Arbeitswiderstand RA, der in der Praxis den Ausgangswiderstand der Schaltung bestimmt. Der ausgangsseitige Kollektorstrom IC wird vom vergleichsweise kleineren Basisstrom IB gesteuert.

| Abbildung 3.76.: | Emitterschaltung: Eingangs– und Ausgangskennlinien (skizziert nach Hinsch [Hin96]). |

Die Eingangskennlinie gibt das Verhalten der Injektionsdiode wieder; die Ausgangskennlinien zeigen das Sperrstromverhalten der BC–Diode bei IB = 0 bzw. stufenweise angehobenen Kennlinien mit wachsendem IB bzw. UBE. Wird das Kennlinienfeld nach rechts fortgesetzt, folgt der Lawinendurchbruch in der BC–Raumladungszone. Weitere Eigenschaften sind: Ausgangsimpendanz von 10 −100kΩ, nichtlineare Spannungsverstärkung von 20 - 100, sehr lineare Stromverstärkung B von 50 - 500, typisch 100, grosse Steilheit, Durchbruch 2. Art (posiviter Temperaturkoeffizient bedeutet inhomogene Stromverteilungen, die zu lokaler Erhitzung und schliesslich zur lokalen Zerstörung insbesonders von Leistungs– und Hochspannungstransistoren führen).

Ein Schalter benötigt zwei klar unterscheidbare, verlustarme Zustände. Der Normalzustand (in Abbilding 3.77 mit 1 bezeichnet) zeigt erhebliche Verluste und wird bei der Verwendung des Transistors als Schalter nur als Zwischenzustand durchlaufen. Der Zustand ‘Zu’ oder ‘Aus’ wird erreicht, indem IB ≈ 0 gemacht wird. Dann sinkt UBE unter die Durchlassspannung (UBE < US ≈ 0, 6V) und IC sinkt auf einen minimalen Restbetrag ab. Der Widerstand des völlig gesperrten Transistors ist maximal und gross gegen den vorgeschalteten Kollektorwiderstand RC, d. h. die Versorgungsspannung UB fällt praktisch am Transistor ab: UA ≈UB.

Der Zustand ‘Auf’ oder ‘Ein’ wird durch sprungartiges Anlegen einer Spannung an den vorgeschalteten Basiswiderstand RB erreicht, so dass IB so gross wird, dass der Sättigungszustand (Punkt 2 in der Abbildung) erreicht wird. Dabei ist UCE,Sättigung ≈ 0, 2 −0, 5V, also kleiner als UBE: D. h. UCB wird umgepolt und die (bislang immer gesperrte) B–C–Diode wird (erstmals) leitend.

Das zeitliche Schaltverhalten wird natürlich durch das Umladen der Sperrschichtkapazitäten bedingt. Es treten beim Ein– und Ausschalten Verzögerungszeiten auf. (Setzt man eine Schottkydiode so zwischen Basis und Kollektor, dass ihre Anode mit der Basis verbunden ist, lassen sich diese Verzögerungszeiten deutlich verringern: Schottky–TTL–Technologie).

Die Herstellung der Bipolartransistoren erfolgt wieder in Planartechnik.

| Abbildung 3.78.: | Querschnitt und Dotierprofil des vertikalen npn–Bipolartransistors, schematisch (skizziert nach Roulston [Rou99]). |

Der vertikale npn–Bipolartransistor ist in Abbildung 3.78 gezeigt. Im Querschnitt ist mittig der Emitterkontakt zu sehen, daran schliessen beidseitig zwei Basiskontakte an. Die Breiten der Raumladungszonen stehen i. allg. im Verhältnis von etwa 1:2; die BC–Raumladungszone beträgt heute bei High–speed–Transistoren etwa 100 nm, bei Hochspannungstransistoren ca. 10 μm. Der n–dotierte Kollektor wurde auf ein n+–dotiertes Substrat aufgewachsen. Für die Fertigung integrierter vertikaler npn–Transistoren muss der Kollektor ebenfalls an die Oberfläche geführt werden. (Der Emitter sitzt in einer p–dotierten Basiswanne, die im n–dotierten Kollektorgebiet eingelassen ist, das Substrat ist p−–dotiert, die ohmschen Kontakte sind aus Polysilizium). Die Herstellung eines pnp–Transistors erfolgt analog, die Anordnung ist etwas einfacher: lateraler pnp–Transistor. . Die Flächengrössen eines Transistors hängen vom Verwendungszweck ab. Für kleine Spannungen benötigt man heute < 1μm, für einen 600 V–Schalttransistor beispielsweise Ø > 10mm. Der Abstand der Raumladungszonen ist kritisch, eine weitere Verkleinerung der I2L, der integrated injection logic, scheint technisch kaum möglich.

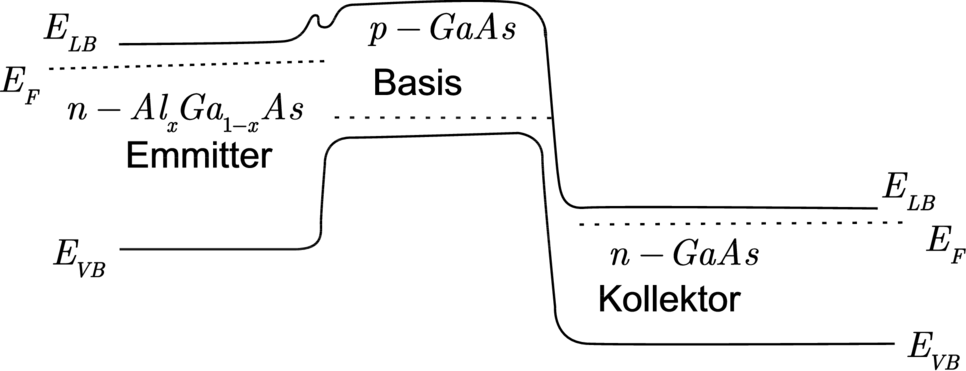

HBT Hetero–Bipolartransistor (Heterjunction

Bipolar Transistor)

Beim konventionellen Bipolartransistor konnte die

Leitfähigkeit der Basis zur Erzielung einer höheren

Diffusionsgeschwindigkeit durch weitere Dotierung nicht

gesteigert werden, weil der Rückstrom von Löchern von

der Basis und dem Emitter dadurch zunahm und der

Emitter–Injektionswirkungsgrad (durch Rekombination)

absank.

Für HF– und Hochgeschwindigkeits–Schalt–Anwendungen kann man diese Grenze durch zwei Schritte hinausschieben.

| Abbildung 3.79.: | AlGaAs–GaAs–Hetero–Bipolartransistor: Elektronisches Bandschema (skizziert nach Sze [Sze81]). |

Erstens kann man das n–dotierte Emittermaterial durch ein ebenfalls n–dotiertes Halbleiter–Material grösserer Bandlücke ersetzen. Die Valenzband–Diskontinuität am Heterokontakt vermindet das Eindringen der Löcher in das Emittergebiet sehr effektiv. Die Basis kann dadurch höher dotiert werden als der Emitter.

In einem weiteren, auf Si–Wafern aufgewachsenen System kann eine ähnliche Physik realisiert werden: Si/SiGe–Bipolartransistor. Hier hat die Basis eine kleinere Energielücke als das Emitter– und Kollektormaterial.

In diesem System ist auch der zweite Verbesserungsschritt realisiert worden, nämlich die ‘Graded base band gap technique GBT’. Hier besitzt die Basis zum einen wie in den Drifttransistoren eine inhomogene Dotierung und zusätzlich (neu) eine ortsabhängige Bandlücke, die ein hohes Driftfeld (15 kV/cm) hervorruft. Dies wird möglich, da mit der Variation des zulegierten Ge–Anteils in einem gewissen Rahmen die kontinuierliche Variation der Energielücke möglich ist. Die Elektronen brauchen zum Durchqueren der z. B. 50 nm breiten Basis noch weniger Zeit. Abschneidefrequenzen von rund 100 GHz sind so erreicht worden und die künftige Verbindung mit der ULSI (Ultra Large Scale Integration)–Technik eröffnet neue Horizonte.

Bestrahlt man Halbleiter–Material mit Licht geeigneter Wellenlänge, so wird seine Leitfähigkeit (Dunkelleitfähigkeit) erhöht um die sog. Fotoleitfähigkeit. Dabei werden i. allg. die Ladungsträgerdichten erhöht, während die Ladungsträgerbeweglichkeiten praktisch unverändert bleiben.

Licht kann also in Fotostrom umgewandelt werden: innerer Fotoeffekt oder innerer lichtelektrischer Effekt. Auch die Umkehr ist möglich und dient der Erzeugung von inkohärentem oder kohärentem Licht. Die Anwendungsfelder sind riesig; sie umfassen die Sensorik, die Energietechnik, die kommerzielle Elektronik und die Telekommunikation etc. Glasfasernetze mit ultraniedrigen Verlusten verbinden die Kontinente; längst gibt es die integrierte Optoelektronik. Wir wollen uns hier aber auf die Grundlagen beschränken.

Aus den Absorptionsmessungen am intrinsischen Halbleiter–Material weiss man, dass die Photonen eine Mindestenergie benötigen, um ein Elektron–Loch–Paar über die Bandlücke anzuregen. (Im Halbleiter ist die optische Aktivierungsenergie gleich der thermischen.) Für die Grenzwellenlänge gilt:

![--1,24---

λGr[μm ] = Egap[eV].](phys_elektr676x.png) | (3.13) |

Dabei ist die Wahrscheinlichkeit für einen sog. indirekten Übergang (mit einer Änderung des Quasiimpulses des Elektrons durch ein Phonon) auch bei Raumtemperatur um Grössenordnungen kleiner als für einen direkten. Es liegt die ‘Grundgitter–Fotoleitung’ vor.

Bei dotierten Halbleiter–Materialien werden die vorhandenen Donatoren oder Akzeptoren ionisiert; die sog. Ausläuferabsorption setzt also schon bei grösseren Wellenlängen ein und führt zur sog. ‘Störstellen–Fotoleitung’. Dieser Fotoleitungstyp ist unipolar, während die Grundgitter–Fotoleitung im Prinzip bipolar ist. (Ungleiche Beweglichkeiten und Lebensdauern können jedoch zu einer Unipolarität führen.)

Die aus dem thermischen Gleichgewicht durch Bestrahlung

zusätzlich erzeugten Ladungsträger haben eine mittlere

Lebensdauer, nach der sie wieder rekombinieren. Die

Rekombination legt letzlich fest, ob zwischen Fotoleitfähigkeit

und Beleuchtungsstärke ein linearer Zusammenhang besteht

(oder etwa ∼ ).

).

Der einfachste Fotodetektor ist ein beidseitig kontaktierter Halbleiter–Dickfilmstreifen; unter Beleuchtung erniedrigt sich sein Widerstand. Im sichtbaren Bereich langjährig bewährte Fotowiderstände sind CdS und CdSe. Sie sind hochohmig, sehr empfindlich und sehr langsam.

Aufwendiger sind Fotodioden. In das Absorptionsgebiet

dicht unter der Oberfläche wird eine möglichst ausgedehnte

Raumladungszone gelegt. Bei der klassischen pn–Fotodiode ist

dies ein stark asymmetrisch dotierter pn–Übergang, bei der

pin–Fotodiode ein ausgedehnter intrinsischer Zwischenbereich.

Die Übergänge werden natürlich in Sperrrichtung betrieben,

um die Raumladungszonen möglichst zu verbreitern, die

Stärke des Driftfeldes ist von sekundärer Bedeutung. Für das

Zeitverhalten sind aber neben den internen Laufzeiten

(dotierkonzentrationsabhängig) die Umladezeiten der

Sperrschichtkapazität massgebend. Wegen C ∼ 1∕ ist es

sinnvoll, bei der maximalen Sperrspannung (ca. …10 V)

zu arbeiten; die Schaltzeiten liegen dann bei ca. 10 ns.

PIN–Dioden sind hier wegen ihrer kleineren Kapazität

grundsätzlich im Vorteil, Schaltzeiten bis hinab zu 100 ps sind

möglich. Die häufigst verwendeten Materialien sind Si, Ge

und GaAs.

ist es

sinnvoll, bei der maximalen Sperrspannung (ca. …10 V)

zu arbeiten; die Schaltzeiten liegen dann bei ca. 10 ns.

PIN–Dioden sind hier wegen ihrer kleineren Kapazität

grundsätzlich im Vorteil, Schaltzeiten bis hinab zu 100 ps sind

möglich. Die häufigst verwendeten Materialien sind Si, Ge

und GaAs.

Prinzipiell sind alle Halbleiter–Kontakte mit ihren jeweiligen Raumladungszonen zur Detektion von Licht (oder härterer Strahlung) geeignet: die Schottkydiode, die Metall–I–N–Diode, die MOS–Diode. Die Heteroepitaxiemethoden ermöglichen neuartige Bauelemente, in denen Absorptionsgebiet und Speichergebiete räumlich getrennt sind.

Mit einer von aussen angelegten Sperrspannung detektiert man einen Fotostrom. Ohne Vorspannung fliesst bei Kurzschluss ein ‘Kurzschluss–Strom’ beziehungsweise erzeugt die Fotodiode bei offenen Kontakten eine Spannung. Abhängig von der Bauform spricht man von Fotoelement oder von der Solarzelle.

Die bisher genannten Bauelemente funktionieren ohne Verstärkung. Innere Verstärkung bis Faktoren von 104 kann man in Avalanche Fotodioden (Lawinen–Fotodioden) erreichen. Durch geeignete Dotierung und hohe Sperrspannungen werden in diesem Element Ladungsträger bewusst durch lokale Stossionisation und weniger durch Beleuchtung erzeugt, im Driftfeld beschleunigt und so ein Lawinendurchbruch gezündet. Meist weist die Diode eine P+P−PN+–Struktur auf, es kann aber auch ein Metall-Halbleiter–Kontakt oder eine PIN–Struktur, etc. sein. Die Anstiegszeiten können unter 100 ps liegen.

Eine sehr effektive, lineare Möglichkeit zur Verstärkung bieten die Fototransistoren. Beim bipolaren Transistor ist die gesperrte Basis–Kollektor–Diode das Absorptionsgebiet. Die Löcher erhöhen die Basis–Emitter–Spannung, so dass der Emitter mehr Elektronen in die Basis und damit in den Kollektor injiziert. Die Bipolar–Fototransistoren sind allerdings langsam (ca. 100 kHz). Beim Sperrschicht–Feldeffekt–Fototransistor und beim MOSFET–Fototransistor werden bevorzugt die breiten Sperrzonenbereiche beleuchtet. Hervorzuheben ist beim ersten Typ die Rauscharmut, beim zweiten die kurzen Ansprechzeiten.

Solarzellen sind besondere Bauelemente; kein kommerzielles Detektorelement wurde so sehr auf Effizienz, Grossflächigkeit und Preiswertheit optimiert. Sie gibt es in einer Vielzahl von Bauformen, meist aus Si. Einkristalline Solarzellen haben Wirkungsgrade von über 26% erreicht.

pn–Dioden aus Halbleitern mit direkter Bandlücke emittieren Strahlung, wenn sie in Durchlassrichtung betrieben werden: LED (Light emitting diode). Die Ursache ist die sog. strahlende direkte Rekombination über die Bandlücke hinweg. GaAs selbst emittiert im Infratoren, im Sichtbaren werden GaAs1−xPx–Materialien und GaP:N–Materialien eingesetzt. Neuerdings spielt GaN eine bedeutende Rolle. Das Emissionsspektrum ist i. allg. sehr breit und temperaturabhängig. Die Richtcharakteristik ist ausgesprochen breit und wird in der Praxis z. B. durch Kunststofflinsen in Vorwärtsrichtung verbessert. Die Schaltzeiten können 1 μs deutlich unterschreiten.

Die strahlende Rekombination kann auch über einen Zwischenzustand (Lumineszenz–Zentrum) erfolgen. Bekanntes Beispiel sind die blauen SiC–LEDs (Siemens). Die neuen blauen LEDs bestehen aus AlGaN/InGaN–Doppelheterostrukturen. Werden sie mit YAG (Yttrium Aluminium Garnet) und Phosphoren direkt beschichtet, entsteht eine weisse LED. Ein weiterer Trend geht zu grossflächigen LEDs, einzelne Emitterflächen reichen an 1mm2.

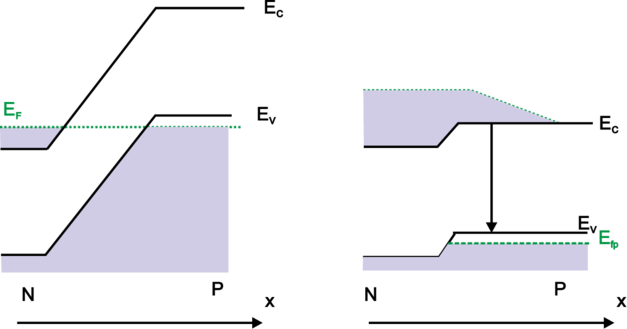

Das LED–Prinzip lässt sich zum Halbleiter–Laser weiterentwickeln. Dazu sind zwei Dinge notwendig. Erstens muss die induzierte Emission die bei der LED ausschliesslich vorhandene spontane Emission deulich übertreffen. Hierzu ist in der sog. aktiven Zone eine ausreichende Besetzungsinversion notwendig. In einer beidseitig sehr hoch dotierten (> 1019cm−3) entarteten pn–Diode, die in Durchlassrichtung betrieben wird, ist die Ladungsträgerinjektion tatsächlich ausreichend gross, um gepulsten Laserbetrieb zu erhalten. Vorausgesetzt, die zweite Bedingung ist erfüllt: die gesamten Verluste der Strahlungsmode müssen kleiner sein als ihr Gewinn. Erreicht wird dies durch einen länglichen (ca. 1 mm) Resonator. Man erhält ihn durch Brechen entlang einer niederinduzierten Kristallebene ((110) in GaAs), die Seitenflächen werden aufgeraut. Dieser sog. Kantenstrahler emittiert an beiden Enden.

| Abbildung 3.82.: | P+N+–Laserdiode a) ohne Spannung und b) mit angelegter Spannung und dadurch hervorgerufener Besetzungsinversion. (skizziert nach Roulston [Rou99]) |

Die aktive Zone ist mehrere μm hoch und seitlich noch unbegrenzt; auch die Strompfade sind noch undefiniert. Deshalb ist die sog. Schwellstromdichte noch sehr hoch, die Verlustwärme zerstört die Laserdiode rasch.

Viel besser wäre es, wenn der optische Resonator durch einen Wellenleiter seitlich auf seine Grundmode eingeschränkt würde; das Halbleiter–Material der aktiven Zone müsste also einen deutlich höheren Brechungsindex haben als das sie umgebende Material: ‘optisches Confinement’. Auch der Diodenstrom müsste nur durch die aktive Zone und auf den Zuleitungswegen möglichst niederohmiges Material durchfliessen müssen: ‘Elektrisches Confinement’. Die mässige spektrale Bandbreite, bedingt durch die energetische Breite der besetzten Zustände (hν > Egap !) und die gebrochenen planen Endflächen sollten durch einen wellenlängenselektiven hochreflektierenden Spiegel (z. B. DFB Distributed feedback) ersetzt werden.

Technologisch haben die Halbleiter diesen weiten Weg über viele Jahre mit schrittweisen Verbesserungen zurückgelegt. Hier können nur wenige genannt werden: der Heterojunction Laser, der Doppel–Heterojunction Laser mit dem optischen Confinement in der Senkrechten und einer senkrechten Ausdehnung der aktiven Zone von ca. 200 nm durch ein elektrisches Confinement mit Hilfe der Banddiskontinuitäten.

Abbildung 3.84 zeigt eine weitere verbesserte Variante dieses Typs. Der Wellenleiter ist zusätzlich seitlich begrenzt; der Zuleitungskontakt ist durch eine Oxidmaske streifenförmig definiert. Mit solchen Lasern sind ca. 10 mW im Dauerbetrieb bei Raumtemperatur möglich.

Noch niedrigere Schwellströme erreicht man, wenn die aktive Zone durch einen Single Quantum Well oder gar ein Multiquantum Well gebildet wird. Die hochdefinierte Art und die Höhe der beteiligten Elektronen– und Löcherzustandsdichten ermöglicht unbekannte Verstärkungen (pro aktive Zonenlänge). Mit diesem Konzept konnte z. B. im ZnSe–Materialsystem der erste blaue Dauerstrichlaser bei Raumtemperaur realisiert werden (Nakayama, 1993).

| Abbildung 3.85.: | GaAs–VCSEL für 750 nm, Arbeitsgruppe Ebeling, Universität Ulm. (skizziert nach Ebeling [FE95]) |

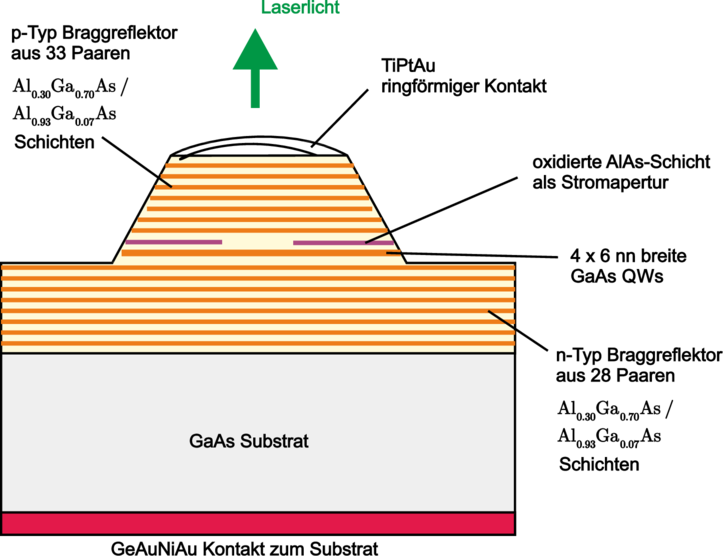

Durch Verwendung mehrerer Quantum Wells und Spiegeln aus Braggreflektoren gelang es schliesslich, VCSELs (Vertical–cavity surface–emitting lasers) zu realisieren. Zum Abschluss sei ein Beispiel der Universität Ulm (Arbeitsgruppe Ebeling) hierzu gezeigt. Vier 6 nm dicke GaAs Quantentöpfe sind zwischen Al0,3Ga0,7–Barrieren eingebettet. Der Laser emittiert einen zylindersymmetrischen Strahl nach oben (top emitting).

Bedingt durch die Dominanz der Silizium–CMOS–Technologie bei den integrierten Schaltungen muss ein Resümee mit einem Blick auf den MOS–Transistor beginnen. Mit jedem Technologieschritt werden seine Abmessungen kleiner und sein Gateoxid immer dünner. Irgendwann zwischen 2010 und 2020, so sagt dies die ‘technology roadmap’ der SIA (Semiconductor Industries Association/USA) voraus, wird die CMOS–Technologie aus physikalischen Gründen nicht mehr anwendbar sein. (Ein Schaltvorgang wird aus Dimensionsgründen nur noch von ca. 10 Elektronen getragen werden. Die Wellenfunktionen des Halbleiters und besonders des Metalls lecken in das Oxid hinaus, so dass mindestens 4 – 5 Oxidmonolagen nötig sind, damit sich Isolatorbandzustände überhaupt ausbilden können.)

Eine ca. 1 nm dicke Gate–Oxidschicht kann von einzelnen Elektronen durchtunnelt werden: Tunneloxid. Darauf beruht die ‘Single electron electronics’, die auf einer Grössenskala < 10nm arbeitet.

In der Grundanordnung befindet sich zwischen 2 Elektroden, jeweils durch Tunnelstrecken getrennt, eine Nanoinsel aus leitendem Material, z. B. ein metallener ‘nanodot’. Die Inselkapazität soll möglichst klein sein (ca. 10−19 −10−18F), d. h. der Partikel darf nur einen Durchmesser von wenigen Nanometer haben.

Bringt man durch einen Spannungsimpuls ein Elektron über die Source–seitige Tunnelstrecke auf die Nanoinsel, so verändert die Ladung des Elektrons die Tunnelverhältnisse für weitere Elektronen; diese sehen eine zusätzliche ‘Barriere’ und ein weiteres Elektron muss zusätzlich die Energie e2∕2C mitbringen, um ebenfalls auf die Nanoinsel tunneln zu können: Coulomb–Barriere. Für Spannungen |V C|> e2∕2C können Elektronen in beide Richtungen transportiert werden, was man durch Messen der I(U)–Kennlinie jeweils überprüfen kann.

Nimmt man eine dritte Elektrode (Gate) hinzu, so kommt man zum SET (Single electron transistor). Es gibt erste Beispiele, die bei Raumtemperatur funktionieren (e2∕2C »k BT) (Siehe auch Abschnitt ??) .

Zum Abschluss sei noch auf eine Merkwürdigkeit hingewiesen. Bei allen elektronischen Bauelementen spielte der Elektronenspin überhaupt keine Rolle. Dies soll sich mit der ‘Spin–Elektronik’ ändern. Allerdings stehen die Konzepte noch auf dem Papier (z. B. eine neue Schaltungslogik), die erfolgreiche experimentelle Realisierung steht noch aus. Packen wir’s an!

Lizenzinformationen

Lizenzinformationen